Investigadores japoneses presentan un nuevo transistor que podría hacer que el hardware neuromórfico sea práctico para la computación de IA.

El campo de la computación neuromórfica está desarrollando sistemas que imitan la arquitectura y la capacidad de cálculo del cerebro humano. Un elemento son los llamados «reservorios» que emulan redes neuronales y se espera que algún día satisfagan la enorme demanda de mayor capacidad de cálculo y velocidad en la investigación y desarrollo de IA.

La idea de los reservorios en la computación neuromórfica proviene del concepto de computación en reservorios. La computación en reservorios es una estructura de red neuronal recurrente (RNN) en la cual la capa recurrente (el «reservorio») se genera de manera aleatoria y no se somete a entrenamiento. En cambio, solo se actualizan los pesos de salida a través del aprendizaje, lo que simplifica el proceso de entrenamiento y lo hace más eficiente.

En la computación neuromórfica, estos reservorios se pueden implementar en diferentes sustratos, como circuitos electrónicos analógicos, sistemas optoelectrónicos o sistemas mecánicos. En este contexto, se utiliza el término «computación en reservorio físico».

Estos reservorios se comportan como redes neuronales que cambian con el tiempo, dependiendo de la interacción y procesamiento de los datos de entrada, y, por lo tanto, son capaces de transformar datos en representaciones de alta dimensión adecuadas para tareas complejas como el reconocimiento de objetos. Sin embargo, en la práctica, estos sistemas requieren un gran número de estados de reservorio, lo cual es difícil de lograr con el hardware actual.

Nuevo transistor duplica los estados del reservorio

Para superar los problemas de compatibilidad, rendimiento e integración de dichos sistemas de memoria, los investigadores japoneses han desarrollado un nuevo transistor. Según el equipo, este avance abre nuevas posibilidades para la computación neuromórfica de alto rendimiento.

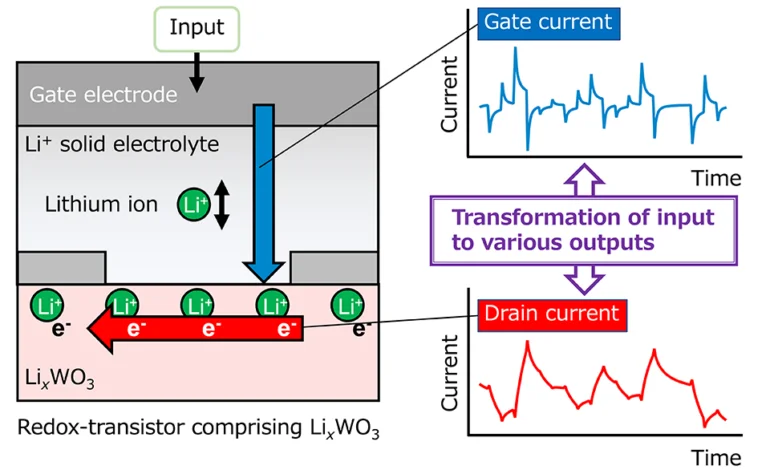

El nuevo transistor del equipo, llamado transistor de reservorio con puerta de iones, puede generar un número récord de estados de reservorio. Según el equipo, el transistor utiliza un electrolito a través del cual los iones de litio se mueven rápidamente, creando dos corrientes de salida y duplicando efectivamente el número de estados de reservorio.

Además, las diferentes tasas de transporte de iones en el canal y el electrolito resultan en una diferencia de tiempo entre dos corrientes, la corriente del drenaje y la corriente de la compuerta. Esta diferencia de tiempo permite que el sistema almacene brevemente información de entradas anteriores y las utilice para operaciones futuras, un requisito esencial para las memorias físicas.

En pruebas, este dispositivo superó a otras tecnologías similares, como los memristores, y demostró ser altamente preciso al hacer predicciones basadas en datos de entradas y salidas anteriores. Según el Dr. Tohru Higuchi, profesor asociado de la Universidad de Ciencias de Tokio (TUS), el sistema tiene el potencial de convertirse en una «tecnología de uso general que se implementará en una amplia gama de dispositivos electrónicos, incluyendo computadoras y teléfonos celulares en el futuro».

Con contenido The Decoder.